本篇文章给各位网友带来的资讯是:发布前夕,英伟达下一代 H100 Hopper 显卡曝光:基于台积电 5nm 的性能怪兽 详情请欣赏下文

IT大王 3 月 22 日消息,Videocardz 又一次在 NVIDIA GTC 前夕泄露了即将推出的 Hopper H100 GPU 的全部内容。IT大王提醒,这是用于数据中心的全新一代 GPU,也是英伟达首款 5nm 产品。

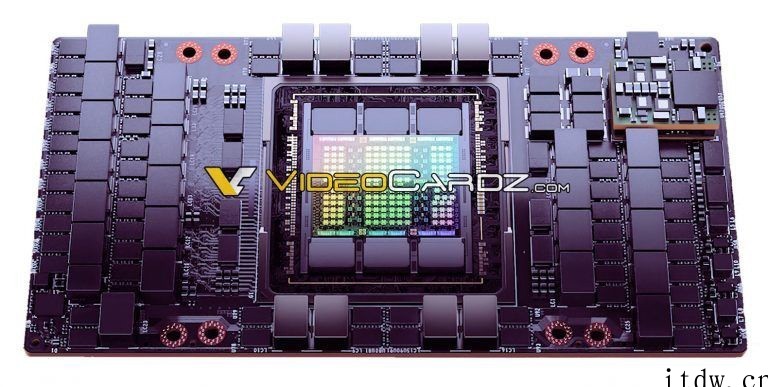

从曝光内容我们可以看到,英伟达新一代 Hopper H100 GPU 仍是一个巨大的单片结构,因此打破了网上关于新一代显卡采用 MCM 设计的猜测,并且可以由此计算的出 144 个单独的流式多处理器 (SM)。

▲ 图为 NVIDIA Hopper GPU,单个芯片,包含 VRM 和 HBM

从图来看,该芯片最多支持 6 个高带宽 HBM 显存堆栈,但由于尚未爆出完整规格,我们无法更进一步的信息。

NVIDIA 也将推出其基于数据中心 / 服务器的新品,外媒认为:

英伟达将推出多款基于 GH100 GPU 的产品,例如用于 DGX 主板的基于 SXM 的 H100 卡、DGX H100 工作站,甚至是 DGX H100 SuperPod。此外,英伟达也将同时发布基于 PCIe 的 H100 产品。

外媒假设,如果其 SM 与 CUDA 核心的比率与图灵卡相同,那么每个 SM 就恰好有 64 个 CUDA 核心,总共就是 9126 个 CUDA 核心;假设其基础主频为 2.2 GHz,这至少可以提供 40 TFLOP 的双精度性能。

此外,PCB 上的 VRM 数量也表明这一款卡的功耗会很大,考虑到有关 Ada Lovelace 的爆料。目前来看,这东西绝对是一头性能猛兽,功耗也是,预计我们将在明天看到 NVIDIA 首席执行官黄仁勋正式将它带到大家面前。

NVIDIA 的 GPU 架构始终以计算机领域的先驱者命名,而这一架构(Hopper)则基于 Grace Hopper(格蕾丝・赫柏 ),她是哈佛 Mark 1 的首批程序员之一,世界最早一批的程序员之一,也是最早的女性程序员之一,也是 Harvard Mark I 上第一个专职程序员,创造了现代第一个编译器 A-0 系统,以及第一个高级商用计算机程序语言“COBOL”,因此也被誉为“COBOL 之母”。

据悉,著名的计算机术语“Debug”(调试排错)便是她的同袍在哈佛二号的继电器上发现一只飞蛾造成短路,才正式成为计算机程序的专有用语。她还是 Y2K 危机的创造者。她培育出许多编程语言专家,被人称为“不可思议的葛丽丝”(Amazing Grace,双关语)。

1、IT大王遵守相关法律法规,由于本站资源全部来源于网络程序/投稿,故资源量太大无法一一准确核实资源侵权的真实性;

2、出于传递信息之目的,故IT大王可能会误刊发损害或影响您的合法权益,请您积极与我们联系处理(所有内容不代表本站观点与立场);

3、因时间、精力有限,我们无法一一核实每一条消息的真实性,但我们会在发布之前尽最大努力来核实这些信息;

4、无论出于何种目的要求本站删除内容,您均需要提供根据国家版权局发布的示范格式

《要求删除或断开链接侵权网络内容的通知》:https://itdw.cn/ziliao/sfgs.pdf,

国家知识产权局《要求删除或断开链接侵权网络内容的通知》填写说明: http://www.ncac.gov.cn/chinacopyright/contents/12227/342400.shtml

未按照国家知识产权局格式通知一律不予处理;请按照此通知格式填写发至本站的邮箱 wl6@163.com