本篇文章给各位网友带来的资讯是:PCIe 6.0 首批芯片设计套件发布,可供开发者使用 详情请欣赏下文

IT大王 11 月 5 日消息,在 PCI SIG 发布 PCIe 6.0 规范最终草案几周后,Cadence 推出了业界首批经过验证的 IP 封装之一,使芯片开发人员能够在他们的设计中实现 PCIe 6.0 支持并对其进行测试。

该 IP 现已上市,早期使用者能够在 2022 年至 2023 年的芯片中添加对 PCIe 6.0 的支持。

“早期采用者已经开始探索新的 PCIe 6.0 规范,我们期待看到他们通过台积电和 Cadence 技术取得积极成果,”Cadence 公司副总裁兼 IP 集团总经理 Sanjive Agarwala 在一份声明中表示。

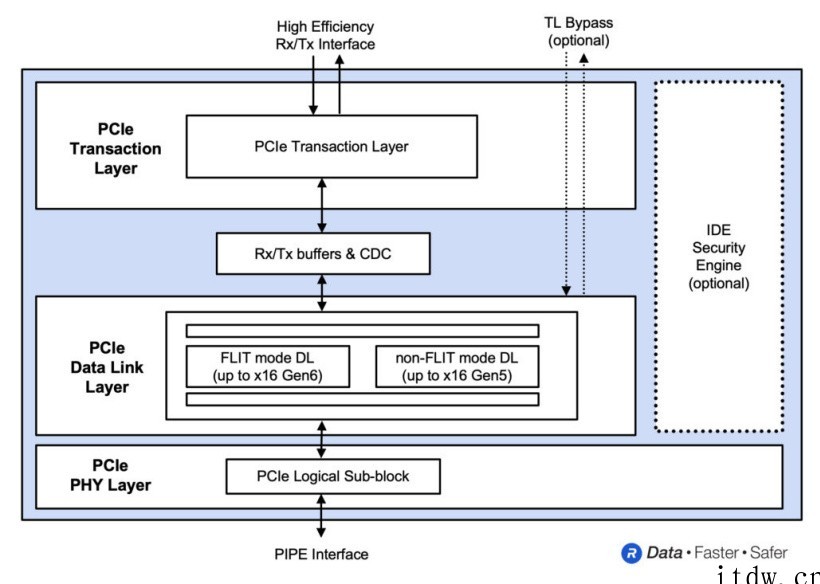

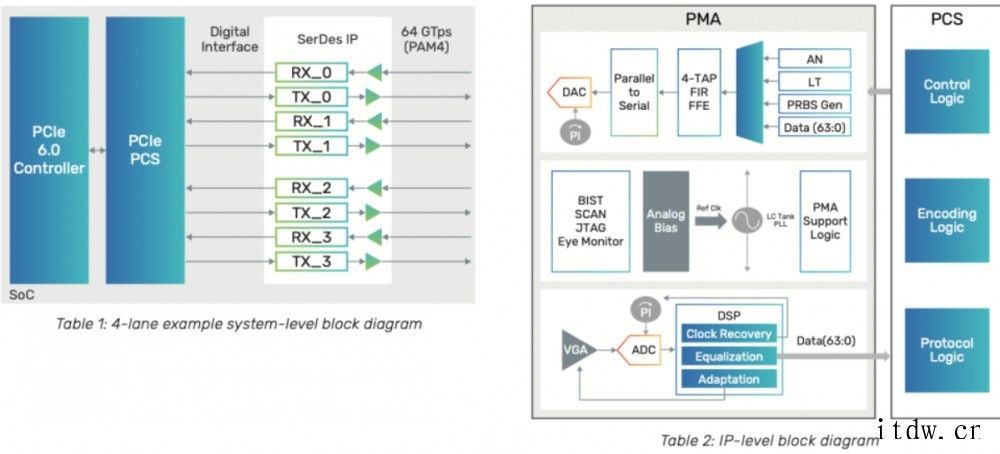

Cadence 的 PCIe 6.0 IP 包含一个控制器和一个基于 DSP 的 PHY(物理接口)。该控制器采用多数据包处理架构,在 x16 配置中支持高达 1024 位宽的数据路径,并支持 PCIe 6.0 的所有关键特性,例如高达 64 GT/s 的数据传输速率(双向)、四级脉冲幅度调制 (PAM4) 信号、低延迟前向纠错 (FEC)、FLIT 模式和 L0p 功率状态。

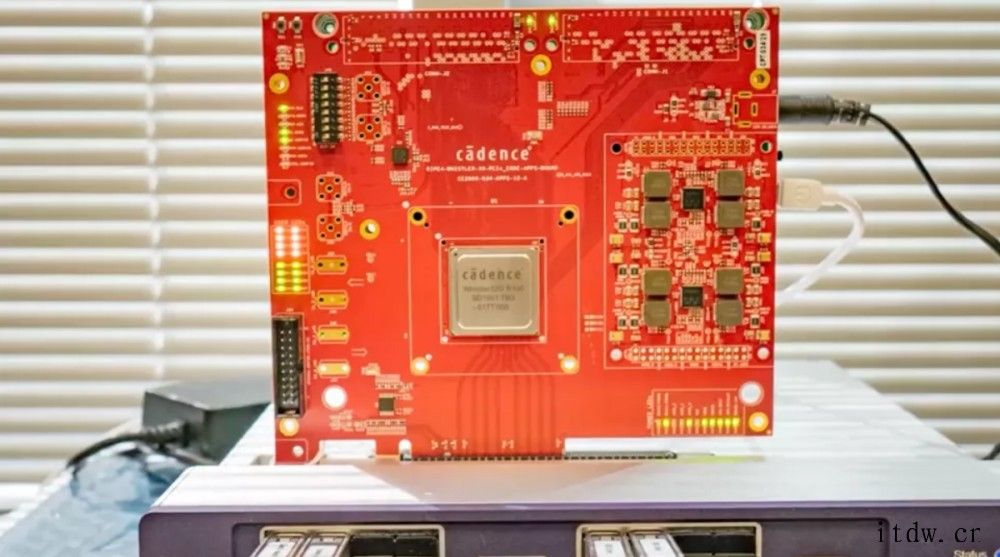

IT大王了解到,该 IP 专为台积电的 N5 节点设计,可供各种 AI/ML/HPC 加速器、图形处理器、SSD 控制器和其他需要支持 PCIe 6.0 的高带宽 ASIC 的开发人员使用。

除了 IP 封装外,Cadence 还提供了使用 N5 实现的 PCIe 6.0 测试芯片,旨在测试所有数据速率下 PCIe 6.0 实现的信号完整性和性能。

该芯片包含一个 PAM4/NRZ 双模发射器,可保证提供最佳信号完整性、对称性和线性度以及低抖动,以及一个可以承受 64GT/s 时超过 35dB 的信号损伤和通道损耗的接收器,以提供复杂的数据恢复功能。

1、IT大王遵守相关法律法规,由于本站资源全部来源于网络程序/投稿,故资源量太大无法一一准确核实资源侵权的真实性;

2、出于传递信息之目的,故IT大王可能会误刊发损害或影响您的合法权益,请您积极与我们联系处理(所有内容不代表本站观点与立场);

3、因时间、精力有限,我们无法一一核实每一条消息的真实性,但我们会在发布之前尽最大努力来核实这些信息;

4、无论出于何种目的要求本站删除内容,您均需要提供根据国家版权局发布的示范格式

《要求删除或断开链接侵权网络内容的通知》:https://itdw.cn/ziliao/sfgs.pdf,

国家知识产权局《要求删除或断开链接侵权网络内容的通知》填写说明: http://www.ncac.gov.cn/chinacopyright/contents/12227/342400.shtml

未按照国家知识产权局格式通知一律不予处理;请按照此通知格式填写发至本站的邮箱 wl6@163.com