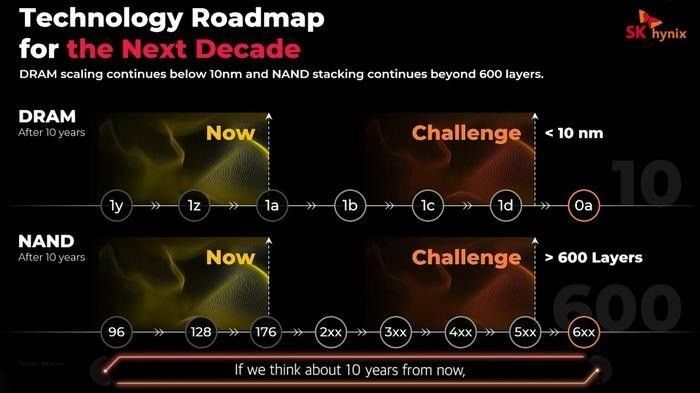

3月28日消息 在近期的 IEEE 国际性稳定性物理学讨论会上,SK 海力士共享了其最近和将来的技术性总体目标企业愿景。SK 海力士觉得,根据将叠加层数提升到 600 层之上,能够再次提升 三维 NAND 的容积。除此之外,该企业有信心依靠极紫外线(EUV)光刻工艺将 DRAM 技术性拓展到 10nm 下列,及其将运行内存和逻辑性集成ic融合到同一个机器设备中,以解决持续提升的工作中负荷。

SK 海力士CEO李锡熙说:“大家已经改善 DRAM 和 NAND 各行各业的技术性发展趋势需要的原材料和设计方案构造,并逐渐处理稳定性难题。假如为此为基本,并获得自主创新,未来有可能完成 10nm 下列的 DRAM 加工工艺和层叠 600 层之上的 NAND。”

三维 NAND 将来将做到 600 层之上

历史时间的工作经验早就证实,三维 NAND 不论是在特性或是在可扩展层面,全是一种十分高效率的系统架构,因而,SK 海力士将在未来两年再次应用它。早在 2020 年 12 月,SK 海力士就发布了具备 1.8Gbps 插口的 176 层 三维 NAND 储存器,且早已逐渐和 SSD 控制板生产商一起开发设计 512GB 的 176 层数据存储器,预估在 2022 企业年会根据新式 三维 NAND 储存器开展驱动器。

就在两年前,该企业觉得能够将 三维 NAND 拓展到 500 层上下,可是如今它早已有信心能够在没多久的未来将其拓展到 600 层之上。伴随着叠加层数的提升,SK 海力士及其别的 三维 NAND 制造商迫不得已让每一层越来越更薄,NAND 模块更小,并引进新的电解介质原材料来维持匀称正电荷,进而维持稳定性。

SK 海力士早已是分子层堆积行业的管理者之一,因而其下一个总体目标是完成深奥长宽比(A/R)触碰(HARC)离子注入技术性。一样,针对 600 层之上的 三维 NAND,很有可能还必须学好如何把双层圆晶层叠起來。

领域什么时候才可以有 600 层之上的 三维 NAND 机器设备及其这般令人震惊的叠加层数将产生的多少的容积,SK 海力士沒有得出实际预测分析,但是该企业仅凭着 176 层技术性就早已紧紧围绕 1TB 的商品,因而 600 层之上的商品容积将是极大的。

DRAM 的将来:EUV 小于 10nm

与美光科技不一样,SK 海力士觉得选用 EUV 光刻工艺是维持 DRAM 特性持续提升,另外提升数据存储器容积、操纵功能损耗最立即的方式。依靠 DDR5,该企业迫不得已发布容积超出 16GB 的储存设备,数据信息传输速度可以达到 6400GT/s,这种储存设备将层叠在一起以搭建大空间的 DRAM。

因为将来的储存器商品务必达到性能卓越、高容及其功耗等规定,因而优秀的生产技术越来越更为关键。为了更好地取得成功执行 EUV 技术性,SK 海力士已经开发设计用以平稳 EUV 图案设计和缺陷管理的新型材料和光刻技术。此外,该企业已经寻找新的充电电池构造,另外根据应用由高相对介电常数原材料做成更薄的的电解介质来维持其电容器。

特别注意的是,SK 海力士如今也在找寻降低 “用以互联的金属材料”电阻器的方式,这说明 DRAM 晶体三极管的规格早已越来越十分小,以致于其接触点将变成短板。依靠 EUV,晶体三极管将变小规格,提高特性并降低功耗,回路电阻将变成 10nm 下列的短板。不一样的集成ic生生产商用不一样的方法来处理这一难题:intel决策应用钴替代钨,而tsmc和三星则挑选了可选择性钨堆积加工工艺。SK 海力士未详细描述其抗回路电阻的方式,仅仅说明已经寻找下一代电级和绝缘层材料并引进新技术新工艺。

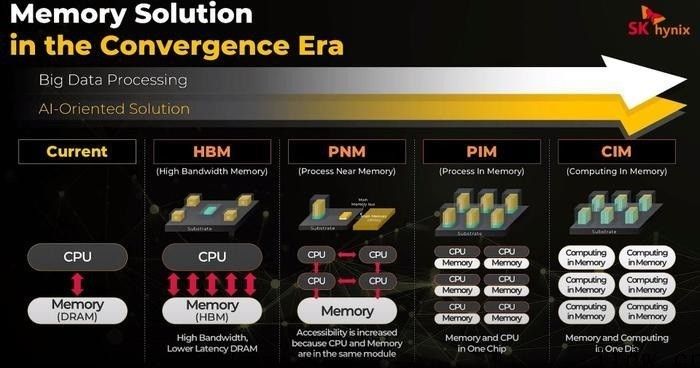

结合解决和运行内存的近运行内存解决

除开使 DRAM 速率迅速并提升容积外,SK 海力士还希望结合运行内存和解决技术性。现如今,用以高性能计算机的顶尖CPU应用根据插进器联接到他们的带宽测试(HBM),SK 海力士将此定义称作 PNM(近运行内存解决),并肯定下一步将是CPU和运行内存存有于单独封裝中的 PIM(运行内存中解决),而该企业最后将找寻 CIM(运行内存中测算),将 CPU 和运行内存集成化到一起。

SK 海力士的 CIM 在非常大水平上与2020年 2 月发布的三星 PIM(运行内存解决)定义类似,并很有可能达到 HJEDEC 界定的行业标准。三星的 HBM- PIM 将以 300MHz 运作的 32 个适用 FP16 的可编程控制器测算模块(PCU)置入到 4gB 运行内存裸片中。能够应用基本储存指令操纵 PCU,并实行一些基本上测算。三星宣称其 HBM-PIM 运行内存早已在领跑的 AI 解决方法服务提供商的 AI 网络加速器中开展了实验,该技术性能够应用 DRAM 生产制造加工工艺生产制造,针对不用高精密但能够从总数诸多的简单化核心中获益的 AI 和别的工作中负荷实际意义重特大。

现阶段尚不清楚 SK 海力士是不是将依据三星明确提出的将要公布的 JEDEC 规范执行 CIM,或是选用特有技术性,但能够明确的是,世界最大的 DRAM 生产商对结合的储存器和逻辑设备都抱有类似的企业愿景。

逻辑性和运行内存的结合针对利基运用十分更有意义,另外,也有大量普遍的应用软件能够从运行内存,储存和CPU更密切的集成化中获益。因此,SK 海力士已经开发设计密切集成化异构计算互联封裝技术性,这种封裝包括解决 IP、DRAM、NAND、微机电系统(MEMS)、射频识别技术(RFID)和各种各样感应器。但是,该企业并未出示很多详细资料。

1、IT大王遵守相关法律法规,由于本站资源全部来源于网络程序/投稿,故资源量太大无法一一准确核实资源侵权的真实性;

2、出于传递信息之目的,故IT大王可能会误刊发损害或影响您的合法权益,请您积极与我们联系处理(所有内容不代表本站观点与立场);

3、因时间、精力有限,我们无法一一核实每一条消息的真实性,但我们会在发布之前尽最大努力来核实这些信息;

4、无论出于何种目的要求本站删除内容,您均需要提供根据国家版权局发布的示范格式

《要求删除或断开链接侵权网络内容的通知》:https://itdw.cn/ziliao/sfgs.pdf,

国家知识产权局《要求删除或断开链接侵权网络内容的通知》填写说明: http://www.ncac.gov.cn/chinacopyright/contents/12227/342400.shtml

未按照国家知识产权局格式通知一律不予处理;请按照此通知格式填写发至本站的邮箱 wl6@163.com